# Ratings, Specifications and Waveforms for FACT Data Sheets

#### ON Semiconductor®

http://onsemi.com

#### APPLICATION NOTE

# **Specifying FACT Devices**

Traditionally, when a semiconductor manufacturer completed a new device for introduction, specifications were based on the characterization of just a few parts. While these specifications were appealing to the designer, they were often too tight and, over time, the IC manufacturers had difficulty producing devices to the original specs. This forced the manufacturer to relax circuit specifications to reflect the actual performance of the device.

As a result, designers were required to review system designs to ensure the system would remain reliable with the new specifications. Motorola realized and understood the problems associated with characterizing devices too aggressively.

To provide more realistic and manufacturable specs, Motorola devised a systematic and thorough process to generate specifications. Devices are selected from multiple wafer lots to ensure process variations are taken into account. In addition, the process parameters are measured and compared to the known process limits.

This method of characterizing parts more accurately represents the product across time, voltage, temperature and process rather than portraying the fastest possible device. FACT circuits are therefore guaranteed to be manufacturable over time without the need to respecify timing.

These specification guidelines allow designers to design systems more efficiently since the devices used will behave as documented. Unspecified guardbands no longer need to be added by the designer to ensure system reliability.

# Power Dissipation — Test Philosophy

In an effort to reduce confusion about measuring  $C_{PD}$ , a JEDEC standard test procedure (per JEDEC, Appendix E) has been adopted which specifies the test setup for each type of device. This allows a device to be exercised in a consistent manner for the purpose of specification comparison. All device measurements are made with  $V_{CC} = 5 \text{ V}$  at 25°C, with 3-state outputs both enabled and disabled.

**Gates** — Switch one input. Bias the remaining inputs such that the output switches.

**Latches** — Switch the Enable and D inputs such that the latch toggles.

**Flip-Flops** — Switch the clock pin while changing D (or bias J and K) such that the output(s) change each clock cycle. For parts with a common clock, exercise only one flip-flop.

**Decoders** — Switch one address pin which changes two outputs.

**Multiplexers** — Switch one address pin with the corresponding data inputs at opposite logic levels so that the output switches.

**Counters** — Switch the clock pin with other inputs biased such that the device counts.

**Shift Registers** — Switch the clock pin with other inputs biased such that the device counts.

**Transceivers** — Switch one data input. For bidirectional devices enable only one direction.

Parity Generator — Switch one input.

**Priority Encoders** — Switch the lowest priority input.

**Load Capacitance** — Each output which is switching should be loaded with the standard 50 pF.

If the device is tested at a high enough frequency, the static supply current can be ignored. Thus at 1 MHz, the following formula can be used to calculate  $C_{PD}$ :

$C_{PD} = I_{CC}/(V_{CC}) (1 \times 10^6)$  – Equivalent Load Capacitance

#### AND8277/D

#### **Ratings and Specifications**

| Symbol           | Parameter                                        | Value                        | Unit |

|------------------|--------------------------------------------------|------------------------------|------|

| V <sub>CC</sub>  | DC Supply Voltage (Referenced to GND)            | -0.5 to +7.0                 | V    |

| V <sub>in</sub>  | DC Input Voltage (Referenced to GND)             | -0.5 to V <sub>CC</sub> +0.5 | V    |

| V <sub>out</sub> | DC Output Voltage (Referenced to GND)            | -0.5 to V <sub>CC</sub> +0.5 | V    |

| I <sub>in</sub>  | DC Input Current, per Pin                        | ±20                          | mA   |

| I <sub>out</sub> | DC Output Source/Sink Current, per Pin           | ±50                          | mA   |

| I <sub>CC</sub>  | DC V <sub>CC</sub> or GND Current per Output Pin | ±50                          | mA   |

| T <sub>stg</sub> | Storage Temperature                              | -65 to +150                  | °C   |

<sup>&</sup>lt;sup>1</sup> Absolute maximum ratings are those values beyond which damage to the device may occur. Obviously the databook specifications should be met, without exception to ensure that the system design is reliable over its power supply, temperature, output/input loading variables. Motorola does not recommend operation of FACT circuits outside databook specifications.

Figure 3-1. Absolute Maximum Ratings<sup>1</sup>

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                             | Parameter                                                            |                         | Min | Тур | Max             | Unit |  |

|------------------------------------|----------------------------------------------------------------------|-------------------------|-----|-----|-----------------|------|--|

| V <sub>CC</sub> Supply Voltage     | Overally Mallage                                                     | ′AC                     | 2.0 | 5.0 | 6.0             | V    |  |

|                                    | Supply Voltage                                                       | 'ACT                    | 4.5 | 5.0 | 5.5             |      |  |

| V <sub>in</sub> , V <sub>out</sub> | DC Input Voltage, Output Voltage (Ref. to GND)                       |                         | 0   |     | V <sub>CC</sub> | V    |  |

|                                    | Input Rise and Fall Time (Note 1)  'AC Devices except Schmitt Inputs | V <sub>CC</sub> @ 3.0 V |     | 150 |                 | ns/V |  |

| t <sub>r</sub> , t <sub>f</sub>    |                                                                      | V <sub>CC</sub> @ 4.5 V |     | 40  |                 |      |  |

|                                    | The Devices except estimate inputs                                   | V <sub>CC</sub> @ 5.5 V |     | 25  |                 |      |  |

|                                    | , Input Rise and Fall Time (Note 2)                                  | V <sub>CC</sub> @ 4.5 V |     | 10  |                 | 0.4  |  |

| t <sub>r</sub> , t <sub>f</sub>    | 'ACT Devices except Schmitt Inputs                                   | V <sub>CC</sub> @ 5.5 V |     | 8.0 |                 | ns/V |  |

| TJ                                 | Junction Temperature (PDIP)                                          |                         |     |     | 140             | °C   |  |

| T <sub>A</sub>                     | Operating Ambient Temperature Range                                  |                         | -40 | 25  | 85              | °C   |  |

| I <sub>OH</sub>                    | Output Current — High                                                |                         |     |     | -24             | mA   |  |

| I <sub>OL</sub>                    | Output Current — Low                                                 |                         |     |     | 24              | mA   |  |

<sup>1.</sup>  $V_{in}$  from 30% to 70%  $V_{CC}$ ; see individual Data Sheets for devices that differ from the typical input rise and fall times. 2.  $V_{in}$  from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.

Figure 3-2. Recommended Operating Conditions

### AND8277/D

# DC CHARACTERISTICS for 'AC Family Devices

|                  | Parameter                            | V <sub>CC</sub> (V) | 74AC<br>T <sub>A</sub> = +25°C |                      | 74AC                               | Unit |                                                                                                                       |

|------------------|--------------------------------------|---------------------|--------------------------------|----------------------|------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------|

| Symbol           |                                      |                     |                                |                      | T <sub>A</sub> =<br>-40°C to +85°C |      | Conditions                                                                                                            |

|                  |                                      |                     | Typ Guar                       |                      | anteed Limits                      |      |                                                                                                                       |

| V <sub>IH</sub>  | Minimum High Level<br>Input Voltage  | 3.0<br>4.5<br>5.5   | 1.5<br>2.25<br>2.75            | 2.1<br>3.15<br>3.85  | 2.1<br>3.15<br>3.85                | V    | V <sub>OUT</sub> = 0.1 V<br>or V <sub>CC</sub> – 0.1 V                                                                |

| V <sub>IL</sub>  | Maximum Low Level<br>Input Voltage   | 3.0<br>4.5<br>5.5   | 1.5<br>2.25<br>2.75            | 0.9<br>1.35<br>1.65  | 0.9<br>1.35<br>1.65                | V    | V <sub>OUT</sub> = 0.1 V<br>or V <sub>CC</sub> – 0.1 V                                                                |

| V <sub>OH</sub>  | Minimum High Level<br>Output Voltage | 3.0<br>4.5<br>5.5   | 2.99<br>4.49<br>5.49           | 2.9<br>4.4<br>5.4    | 2.9<br>4.4<br>5.4                  | V    | I <sub>OUT</sub> = -50 μA                                                                                             |

|                  |                                      | 3.0<br>4.5<br>5.5   |                                | 2.56<br>3.86<br>4.86 | 2.46<br>3.76<br>4.76               | V    | $^*$ V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub> $-12 \text{ mA}$ $I_{OH}$ $-24 \text{ mA}$ $-24 \text{ mA}$ |

| V <sub>OL</sub>  | Maximum Low Level<br>Output Voltage  | 3.0<br>4.5<br>5.5   | 0.002<br>0.001<br>0.001        | 0.1<br>0.1<br>0.1    | 0.1<br>0.1<br>0.1                  | V    | Ι <sub>ΟUT</sub> = 50 μΑ                                                                                              |

|                  |                                      | 3.0<br>4.5<br>5.5   |                                | 0.36<br>0.36<br>0.36 | 0.44<br>0.44<br>0.44               | V    | *V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub><br>12 mA<br>I <sub>OL</sub> 24 mA<br>24 mA                      |

| I <sub>IN</sub>  | Maximum Input<br>Leakage Current     | 5.5                 |                                | ±0.1                 | ±1.0                               | μΑ   | $V_I = V_{CC}$ , GND                                                                                                  |

| I <sub>OLD</sub> | †Minimum Dynamic                     | 5.5                 |                                |                      | 75                                 | mA   | V <sub>OLD</sub> = 1.65 V Max                                                                                         |

| I <sub>OHD</sub> | Output Current                       |                     |                                |                      | -75                                | mA   | V <sub>OHD</sub> = 3.85 V Min                                                                                         |

| I <sub>CC</sub>  | Maximum Quiescent<br>Supply Current  | 5.5                 |                                | 8.0                  | 80                                 | μΑ   | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                                              |

<sup>\*</sup> All outputs loaded; thresholds on input associated with output under test.

† Maximum test duration 2.0 ms, one output loaded at a time. Note:  $I_{\text{IN}}$  and  $I_{\text{CC}}$  @ 3.0 V are guaranteed to be less than or equal to the respective limit @ 5.5 V V<sub>CC</sub>.

#### DC CHARACTERISTICS for 'ACT Family Devices

|                  | Parameter                              |                     | 74ACT  T <sub>A</sub> = 25°C |              | 74ACT                           | Unit |                                                                                           |

|------------------|----------------------------------------|---------------------|------------------------------|--------------|---------------------------------|------|-------------------------------------------------------------------------------------------|

| Symbol           |                                        | V <sub>CC</sub> (V) |                              |              | T <sub>A</sub> = -40°C to +85°C |      | Conditions                                                                                |

|                  |                                        |                     | Тур                          | Guar         | anteed Limits                   |      |                                                                                           |

| V <sub>IH</sub>  | Minimum High Level<br>Input Voltage    | 4.5<br>5.5          | 1.5<br>1.5                   | 2.0<br>2.0   | 2.0<br>2.0                      | V    | $V_{OUT} = 0.1 \text{ V}$<br>or $V_{CC} - 0.1 \text{ V}$                                  |

| V <sub>IL</sub>  | Maximum Low Level<br>Input Voltage     | 4.5<br>5.5          | 1.5<br>1.5                   | 0.8<br>0.8   | 0.8<br>0.8                      | V    | $V_{OUT} = 0.1 \text{ V}$<br>or $V_{CC} - 0.1 \text{ V}$                                  |

| V <sub>OH</sub>  | Minimum High Level<br>Output Voltage   | 4.5<br>5.5          | 4.49<br>5.49                 | 4.4<br>5.4   | 4.4<br>5.4                      | V    | I <sub>OUT</sub> = -50 μA                                                                 |

|                  |                                        | 4.5<br>5.5          |                              | 3.86<br>4.86 | 3.76<br>4.76                    | V    | $^{*}V_{IN} = V_{IL} \text{ or } V_{IH}$ $^{-}24 \text{ mA}$ $^{-}0H$ $^{-}24 \text{ mA}$ |

| V <sub>OL</sub>  | Maximum Low Level<br>Output Voltage    | 4.5<br>5.5          | 0.001<br>0.001               | 0.1<br>0.1   | 0.1<br>0.1                      | V    | I <sub>OUT</sub> = 50 μA                                                                  |

|                  |                                        | 4.5<br>5.5          |                              | 0.36<br>0.36 | 0.44<br>0.44                    | V    | $^*V_{IN} = V_{IL} \text{ or } V_{IH}$ $^24 \text{ mA}$ $^1OL$ $^24 \text{ mA}$           |

| I <sub>IN</sub>  | Maximum Input<br>Leakage Current       | 5.5                 |                              | ±0.1         | ±1.0                            | μΑ   | V <sub>I</sub> = V <sub>CC</sub> , GND                                                    |

| $\Delta I_{CCT}$ | Additional Max. I <sub>CC</sub> /Input | 5.5                 | 0.6                          |              | 1.5                             | mA   | $V_{I} = V_{CC} - 2.1V$                                                                   |

| I <sub>OLD</sub> | †Minimum Dynamic                       | 5.5                 |                              |              | 75                              | mA   | V <sub>OLD</sub> = 1.65 V Max                                                             |

| I <sub>OHD</sub> | Output Current                         | 5.5                 |                              |              | -75                             | mA   | V <sub>OHD</sub> = 3.85 V Min                                                             |

| I <sub>CC</sub>  | Maximum Quiescent<br>Supply Current    | 5.5                 |                              | 8.0          | 80                              | μΑ   | $V_{IN} = V_{CC}$ or GND                                                                  |

<sup>\*</sup> All outputs loaded; thresholds on input associated with output under test.

<sup>†</sup>Maximum test duration 2.0 ms, one output loaded at a time.

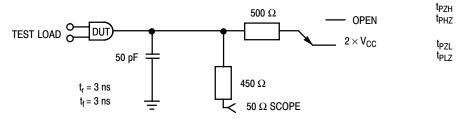

Figure 3-3. AC Tri-State Loading Circuit

# **AC Loading and Waveforms**

#### **Loading Circuit**

Figure 3-3 shows the AC loading circuit used in characterizing and specifying propagation delays of all FACT devices ('AC and 'ACT) unless otherwise specified in the data sheet of a specific device.

The use of this load, differs somewhat from previous (HCMOS) practice, provides more meaningful information and minimizes problems of instrumentation and customer correlation. In the past, +25°C propagation delays for TTL devices were specified with a load of 15 pF to ground; this required great care in building test jigs to minimize stray capacitance and implied the use of high impedance, high frequency scope probes. FAST circuits changed to 50 pF of capacitance allowing more leeway in stray capacitance and

also loading the device during rising or falling output transitions. This more closely resembles the inloading to be expected in average applications and thus gives the designer more useful delay figures. We have incorporated this scheme into the FACT product line. The net effect of the change in AC load is to increase the average observed propagation delay by about 1 ns.

The 500 ohm resistor to ground can be a high frequency passive probe for a sampling oscilloscope, which costs much less than the equivalent high impedance probe. Alternately, the 500 ohm resistor to ground can simply be a 450 ohm resistor feeding into a 50 ohm coaxial cable leading to a sampling scope input connector, with the internal 50 ohm termination of the scope completing the path to ground. This

#### AND8277/D

is the preferred scheme for correlation. (See Figure 3-3.) With this scheme there should be a matching cable from the device input pin to the other input of the sampling scope; this also serves as a 50 ohm termination for the pulse generator that supplies the input signal.

Shown in Figure 3-3 is a second 500 ohm resistor from the device output to a switch. For most measurements this

switch is open; it is closed for measuring one set of the Enable/Disable parameters (LOW-to-OFF and OFF-to-LOW) of a 3-state output. With the switch closed, the pair of 500 ohm resistors and the 2  $\times$  V $_{CC}$  supply voltage establish a quiescent HIGH level.

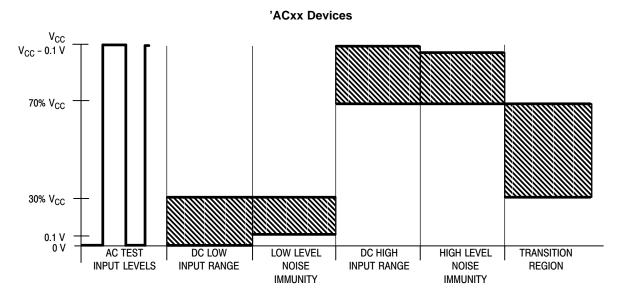

Figure 3-4a. Test Input Signal Levels

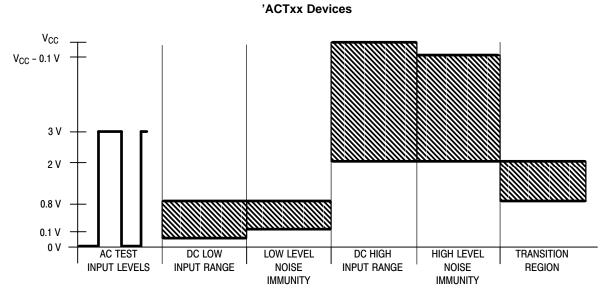

Figure 3-4b. Test Input Signal Levels

# **Test Conditions**

Figures 3-4a and 3-4b describe the input signal voltage levels to be used when testing FACT circuits. The AC test conditions follow industry convention requiring  $V_{IN}$  to range from 0 V for a logic LOW to 3 V for a logic HIGH for 'ACT devices and 0 V to  $V_{CC}$  for 'AC devices. The DC parameters are normally tested with  $V_{IN}$  at guaranteed input levels, that is  $V_{IH}$  to  $V_{IL}$  (see data tables for details). Care must be taken to adequately decouple these high performance parts and to protect the test signals from electrical noise. In an electrically noisy environment, (e.g., a tester and handler not specifically designed for high speed work), DC input levels may need to be adjusted to increase the noise margin to allow for the extra noise in the tester which would not be seen in a system.

Noise immunity testing is performed by raising  $V_{IN}$  to the nominal supply voltage of 5 V then dropping to a level corresponding to  $V_{IH}$  characteristics, and then raising again to the 5 V level. Noise tests can also be performed on the  $V_{IL}$  characteristics by raising  $V_{IN}$  from 0 V to  $V_{IL}$ , then returning to 0 V. Both  $V_{IH}$  and  $V_{IL}$  noise immunity tests should not induce a switch condition on the appropriate outputs of the FACT device.

Good high frequency wiring practices should be used in constructing test jigs. Leads on the load capacitor should be as short as possible to minimize ripples on the output wave form transitions and to minimize undershoot. Generous ground metal (preferably a ground plane) should be used for the same reasons. A V<sub>CC</sub> bypass capacitor should be provided at the test socket, also with minimum lead lengths.

#### **Rise and Fall Times**

Input signals should have rise and fall times of 3 ns and signal swing of 0 V to 3.0 V  $V_{CC}$  for 'ACT devices or 0 V to  $V_{CC}$  for 'AC devices. Rise and fall times less than or equal to 1 ns should be used for testing  $f_{max}$  or pulse widths.

CMOS devices, including 4000 Series CMOS, HC, HCT and FACT families, tend to oscillate when the input rise and fall times become lengthy. As a direct result of its increased performance, FACT devices can be more sensitive to slow input rise and fall times than other lower performance technologies.

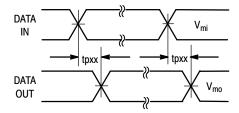

Figure 3-5. Waveform for Inverting and Non-Inverting Functions

It is important to understand why this oscillation occurs. Consider the outputs, where the problem is initiated. Usually, CMOS outputs drive capacitive loads with low DC leakage. When the output changes from a HIGH level to a LOW level, or from a LOW level to a HIGH level, this capacitance has to be charged or discharged. With the present high performance technologies, this charging or discharging takes place in a very short time, typically 2–3 ns. The requirement to charge or discharge the capacitive loads quickly creates a condition where the instantaneous current change through the output structure is quite high. A voltage is generated across the  $V_{\rm CC}$  or ground leads inside the package due to the inductance of these leads. The internal ground of the chip will change in reference to the outside world because of this induced voltage.

Consider the input. If the internal ground changes, the input voltage level appears to change to the DUT. If the input rise time is slow enough, its level might still be in the device threshold region, or very close to it, when the output switches. If the internally-induced voltage is large enough, it is possible to shift the threshold region enough so that it re-crosses the input level. If the gain of the device is sufficient and the input rise or fall time is slow enough, then the device may go into oscillation. As device propagation delays become shorter, the inputs will have less time to rise or fall through the threshold region. As device gains increase, the outputs will swing more, creating more induced voltage. Instantaneous current change will be greater as outputs become quicker, generating more induced voltage.

Package-related causes of output oscillation are not entirely to blame for problems with input rise and fall time measurements. All testers have  $V_{CC}$  and ground leads with a finite inductance. This inductance needs to be added to the inductance in the package to determine the overall voltage which will be induced when the outputs change. As the reference for the input signals moves further away from the pin under test, the test will be more susceptible to problems caused by the inductance of the leads and stray noise. Any noise on the input signal will also cause problems. With FACT logic having gains as high as 100, it merely takes a 50 mV change in the input to generate a full 5 V swing on the output.

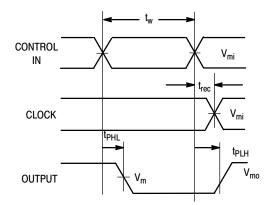

Figure 3-6. Propagational Delay, Pulse Width and t<sub>rec</sub> Waveforms

<sup>\*</sup>  $V_{mi}$  = 50%  $V_{CC}$  for 'AC devices; 1.5 V for 'ACT devices  $V_{mo}$  = 50% for 'AC/'ACT devices

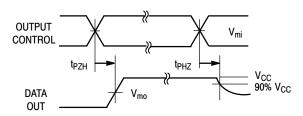

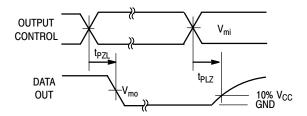

#### **Enable and Disable Times**

Figures 3-8 and 3-9 show that the disable times are measured at the point where the output voltage has risen or fallen by 10% from the voltage rail level (i.e., ground for tPLZ or V<sub>CC</sub> for t<sub>PHZ</sub>). This change enhances the repeatability of measurements, reduces test times, and gives the system designer more realistic delay times to use in calculating minimum cycle times. Since the high impedance state rising or falling waveform is RC-controlled, the first 10% of change is more linear and is less susceptible to external influences. More importantly, perhaps from the system designer's point of view, a change in voltage of 10% is adequate to ensure that a device output has turned OFF. Measuring to a larger change in voltage merely exaggerates the apparent Disable time and thus penalizes system performance since the designer must use the Enable and Disable times to devise worst case timing signals to ensure that the output of one device is disabled before that of another device is enabled.

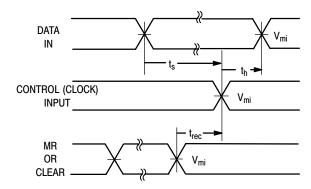

# Propagation Delay, f<sub>max</sub>, Set, Hold, and Recovery Times

A 1 MHz square wave is recommended for most propagation delay tests. The repetition rate must necessarily be increased for testing  $f_{\text{max}}$ . A 50% duty cycle should always be used when testing  $f_{\text{max}}$ . Two pulse generators are usually required for testing such parameters as setup time ( $t_{\text{s}}$ ), hold time ( $t_{\text{h}}$ ), recovery time ( $t_{\text{REC}}$ ) shown in Figure 9.

# **Electrostatic Discharge**

Precautions should be taken to prevent damage to devices by electrostatic discharge. Static charge tends to accumulate on insulated surfaces such as synthetic fabrics or carpeting, plastic sheets, trays, foam, tubes or bags, and on ungrounded electrical tools or appliances. The problem is much worse in a dry atmosphere. In general, it is recommended that individuals take the precaution of touching a known ground before handling devices. To effectively avoid electrostatic damage to FACT devices, it is recommended that individuals wear a grounded wrist strap when handling devices. More often, handling equipment, which is not properly grounded, causes damage to parts. Ensure that all plastic parts of the tester, which are near the device, are conductive and connected to ground.

Figure 3-7. Setup Time, Hold Time and Recovery Time

Figure 3-8. 3-State Output High Enable and Disable Times

Figure 3-9. 3-State Output Low Enable and Disable Times

$^*V_{mi}$  = 50%  $V_{CC}$  for 'AC devices; 1.5 V for 'ACT devices  $V_{mo}$  = 50%  $V_{CC}$  for 'AC/'ACT devices

ON Semiconductor and was registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

860 Toll Free USA/Canada 7 Toll Free USA/Canada Department of the USA/Canada Phone: 421 33 790 2910 Japan Customer Focus One: 81–3–5773–3850

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative